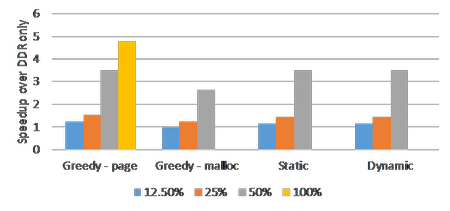

1420 researchers successfully completed a CSSE Level 2 milestone investigating the impact of next-generation multi-level memory hierarchies (i.e., hierarchies including multiple main memory technologies such as high-bandwidth memory and traditional DDR DRAM) on key ASC algorithms and kernels. The study found that while ASC applications vary widely in their ability to make use of higher-bandwidth memory, for some key kernels the high-bandwidth memory increases performance dramatically. Researchers also determined best-paths-forward for managing data movement and allocation between the multiple memory levels. This study will help to shape the use of impending and upcoming DOE procurements including the new Trinity platform. The study also added significant capability in the Structural Simulation Toolkit (SST), enabling node-level architectural simulation of larger-scale and complex codes. Two papers describing some of the results were published in the ACM MEMSYS 2016 conference. Full results were published in a SAND report.